# **Project Monitor Form**

Project: CMS FED

Date: Thur 29 Sept-2005

PMF number: 57

Sheet: 1 of 2

Project Implementation phase.

#### **FED Production**

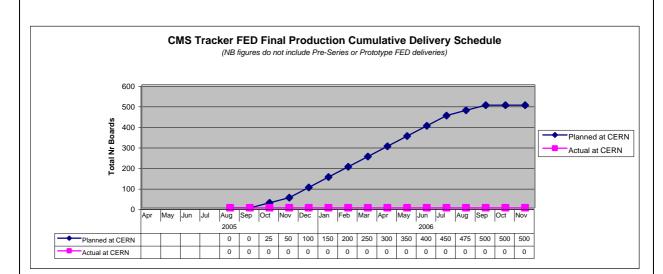

Progress is good. We are slightly ahead of the predicted FED delivery profile shown at last Tracker week (see below).

Now expect to start with delivery to CERN of ~35+ boards in October.

Our special FED Test setups were prepared and fully installed at the Assembly plant in July/August. Their staff were trained by our engineer and are now routinely running the tests, although with some expert assistance from our engineer on request.

The Test bench is working well. Ivan has made a few trips to Calne to help with less obvious problem boards and to pass feedback on minor snags on received boards.

The 1st batch of 50 FED boards was manufactured as planned in August. (first 2 boards were assembled and tested in late July to verify production).

48 have so far passed the Assembly plant tests.

A couple have persistent Bscan problems and will need some rework.

One minor patch to -12V monitor LED has been found necessary.

After some oven tests with dummy modules it was decided by eXception engineers to continue with conventional assembly of ORx modules rather than SMT. It was not found possible to keep within parameters of the solder paste. In addition, they had concerns that ORx could be damaged in subsequent conventional assembly steps as they protrude from the board.

The 2nd batch of 50 boards is now being assembled and some are under test at Calne.

42 of the passed boards are at RAL

**38** of these have now passed our additional tests (ORx input testing, TTC and SLINK). 4 have some problems, which we are investigating. But there are no common faults yet. A further 12 have been dispatched to us.

Results of tests are being archived and backup of disks at Assembly Test bench are being made. Board status is recorded in a production summary <u>spreadsheet</u>.

A short <u>document</u> has been produced summarizing the Acceptance tests to be carried out at RAL. The tests are based on a selection of James' Test suite.

As requested all boards will in addition also be powered overnight.

Our general policy is to put any boards failing tests to one side and go back to them after testing the whole batch. If we spot a systematic failure we would halt production.

Our plan is to continue with tests of the production boards during next 2 weeks.

We would aim to ship between 30 - 40 boards early week of Oct 17th. They should then be there during Tracker week.

Production boards should not be used in Assembly centers.

Meanwhile, for Assembly center needs, we will retest and if ok, send ~ 4 of remaining v2 pre-series asap.

About 150 production boards will be needed for Full Tracker surface tests in B186.

#### **Production Concerns:**

The lead time for the SYSTEM ACE controller (FPGA configuration) has increased ~ 20 weeks? due to disruption at Xilinx fab. We had enough for 125 boards in total. We are investigating obtaining from alternative sources.

#### **Transition Card**

70 cards have been manufactured (using Imperial design files) and all tested ok.

35 of these are now at B904.

Once cards have been verified with final DAQ SLINK system we will place order for remaining 400.

BOM needs minor additions before next production.

### Firmware:

#### VME FPGA:

The problems with VME Block Transfers with both CAEN and SBS are 'fixed' (no problems have yet been reported from CERN or LSA systems).

The SBS BLT read problems, which only showed up in certain crate configurations and was therefore difficult to debug, was traced to a race condition between DTACK and DATA out.

There is still a driver problem with dual processor PCs and CAEN. And possibly with SBS?

The BLT32 readout speed has also now been considerably improved with relatively minor changes to the logic:

Originally (e.g. Lyon DAQ tests): ~ 6 MB/s

Step 1 : Reduced data path in BLT logic => ~ 9 MB/s Step 2 : Speeded up internal clocking => ~13 MB/s

These results are in agreement with measurements made at RAL and by Oz and Costas.

Measuring with a commercial memory card shows limit of ~16-18 MB/s with SBS or CAEN Depending on PCI card arrangement.

To reach this limit with FED would need to introduce a Pre-Fetch mechanism, which is a more major change.

To go beyond this will need to implement MBLT64 (approx doubling of rate). The SBS can't operate in this mode but the CAEN datasheet says it can.

### **DELAY FPGA:**

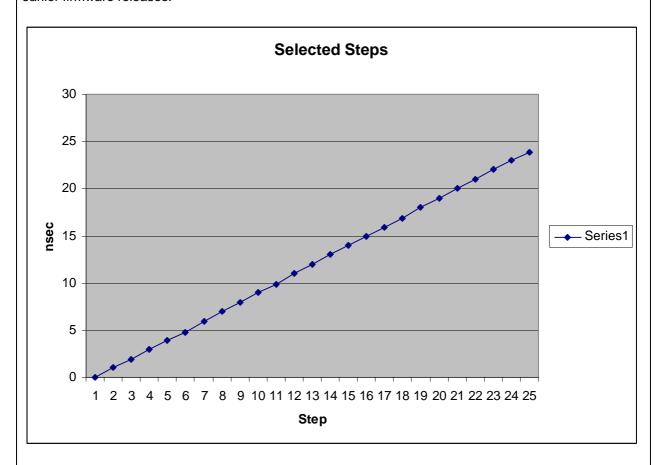

Work has been done to remove the existing discontinuities in the fine skew coverage. By increasing the internal number of fine DCM steps to 64 we can provide a smooth evenly spaced set of 25 x 1 nsec steps.

This will only require a change in the final low level software, but it will NOT be backward compatible with earlier firmware releases.

# FE FPGA:

Further tests with Fake Frame generator have been made with debug software. Final software is needed for use in Tracker DAQ.

ZS-Lite mode (reduced data) has been implemented and some basic tests carried out with debug software. Event data appears correct. Contents of header are still being investigated. Presently the median and codes are removed, but the lengths remain in bytes. To go to absolute minimum data with cluster count will require more major changes.

Selection of the bits to remove when going from 10 bit to 8 bit data has been implemented, but not tested vet.

The VHDL version with all these improvements has to be thoroughly tested with Final Software and Tracker DAQ before it can be released as a new standard.

### REMAINING FIRMWARE & SOFTWARE REQUIREMENTS:

Spy Channel in Frame Finding mode: Needs work in both FE and Delay

Data Buffer Overflow Recovery: Needs work in both FE and BE

Need Final Software to support many new features introduced in past 6 months....

PPD have recruited a new RA.

A document describing the Event Format (based on BE and FE technical descriptions) has been released.

## **Equipment**

3 VME bus extender boards were ordered and expected soon.

TTCoc box Front Panels are now at RAL.

As CERN stores are too slow, an alternative source (in UK) has been found for TTC fibres and couplers.

Oz is organizing equipment for B904.

#### **Other Activities:**

RAL rack water cooling was installed last week and it is now up and running. Ivan is improving the sealing of the racks and is making tests with the Rack turbine. Board temperature measurements are being repeated to find an optimal slot arrangements. However, these tests will need to be finalised using Racks in B904. Some nice display software e.g. Labview would be helpful here.

A firmware module is being introduced which will initialise the Tcrit shutdown temperature at FED power up (as a fail safe).

Safety Training at CERN needs to be done before end of year (for underground access etc).

Agreement with CERN was finally signed in August.