# **Project Monitor Form**

Project: CMS FED

Date: Friday 27 May-2005

PMF number: 55

Sheet: 1 of 2

Project Implementation phase.

### FEDv2

Manufacture of Pre-series Production of 5 + 20 off FEDv2:

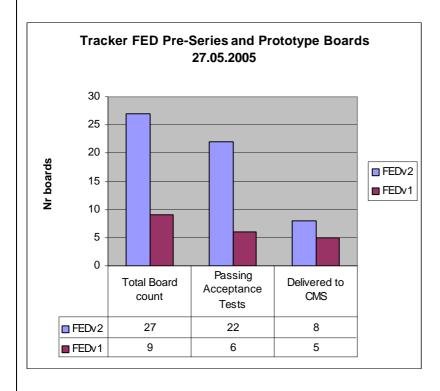

Summary of board status on web.

5 boards still to complete tests.

5 more pre-series boards shipped to CERN today (ser nrs 33-37). Loaded with ACE 06\_05\_05; VME 21\_03\_1D

Meeting was held at eXception Calne on May 25th to review the Pre-Series and plan the final Production.

Reviewed the detailed list of faults found on last 20 boards.

- -LED shorts (due to incorrect part size will be correct on production)

- -Resistor net shorts/opens (part is difficult to assemble, eXception to test with varying solder masks)

Other minor faults

Production plans

ORx to be machine assembled. Samples obtained from CERN for re-profile of ovens.

Circuit schematics and layout unchanged from v2. Minor component values changed. Increase DC converter hole size for conventional assembly. Update drilling drawing. RAL to send updated Design Files, Ordering List. Go to revision PC3205M/3

We will try for the first available assembly slot in July for first production batch of 50 boards. The first couple of boards would be tested at RAL within a 48 hour window (weekend) before giving go ahead for remaining top-side assembly.

### **Full Crate Tests**

The spare LHC crate was eventually received at RAL on 21.04. This crate and the existing FED Tester crate are now installed in the CERN rack. The extender box to interface to the SLINK PC is also working.

Optical splitter board was obtained from Jan and is now installed and working in FED crate. Ivan has made a front panel to support it and will have some more manufactured. More fibres are on order to drive all 16 FEDs.

Before Greg left he was able to successfully release the new adapter card to interface the FED Testers to the TTC system. James' new Multi-FED test software is now running at RAL for full crate tests.

## Results:

Testing with full crate of 16 FEDs. Nothing unexpected seen.

Total power and current ok.

Readout from several boards over VME ok.

Power up ok after mod to resistor on OTemp line (below).

Programming of 16 boot VME EPROMs on chain via J0 backplane card is working.

Temperatures as expected, without water cooling (some boards are powered down if running crate for long periods).

Representative from company providing chiller for water cooling is visiting today.

## **Design Testing:**

The earlier powering and reset problems observed on some boards has been cured by changing a resistor value on the Over Temp shutdown signal. This change will be carried out on all preseries boards and for production.

One of the new FED Kits was loaned from CERN. Using this kit the S-LINK Zero-Suppressed readout on FEDv2 boards are now working without CRC errors under all readout conditions up to 400 M triggers per occupancy setting.

Request from Karl Gill to measure board to board variation in clock propagation delay through TTCrx chips.

### **Transition Cards:**

Final version of Transition card (clock compatible with FEDv2+ only) has also been tested successfully at RAL with pre-series boards.

The length of the final DAQ SLINK CMC Transmitter card has changed slightly from FED Kit version, but still fits on Transition card ok.

A new Front Panel has been designed for final Transition card.

It has been agreed that RAL shall take over responsibility for the procurement of production quantities of the Transition cards. The design files are being handed over to Saeed who will manage this production. Project change order will be required.

# Firmware:

### BE / VME FPGA:

Tested checking of BX synchronisation.

Matt Pearson implemented the low level methods to access the features introduced into the design over the last few months. But he was unable to test them before he left.

Added some more Front Panel LED signals.

Added FED ID register = \$00000fed at fixed location for identifying boards.

Resync command response needs minor updating (remove 21 micro-sec wait) to match new requirements as requested at Resync meeting at CERN 11.05.

### FE FPGA:

Osman has implemented a Fake Frame generator.

Initial tests show that the basic functions are working, but there are some timing adjustments still to be done to obtain to get valid outputs on the first data sample.

Temp sensor I2C readout stopped working in latest VHDL version with Fake Frames.

# **Assembly Plant Testing**

An area on the assembly floor has been set up at for FED testing.

Equipment: Boundary Scan kit is at RAL. PCs are on order.

2 x production 9U crates are expected to be available at CERN by June 8th Arrangements are being made to have these shipped to UK asap. Then need to swap these with existing crates at RAL. This is the critical path item.

Need one more SBS VME bridge (second one at Imperial?)

### **Contracts:**

Good progress has been made recently.

The draft agreement from CERN was received last week. The payment and execution schedules have been updated and some minor amendments have been made by Tony Wells.

A project code is being set up in EID devoted to holding the funds from CERN to cover the payments for the eXception contract.

The final costings for 500 boards have been agreed with eXception with handling charges for the free issue components, including ORx modules.

The production contract document was released to them this week.

An order was placed in advance to purchase long lead items.

### **Forward Look**

Activities, objectives and resources for the next 6 months ...

- Production and acceptance tests in UK.

- How do we exploit/contribute to B904 integration centre?

- Remaining Firmware requirements and associated low level software.

- Higher level software tasks, calibration, run initialisation procedures ...etc

- +++